你是否设计过挠性印制电路?很多经验丰富的PCB布局设计师和电气工程师都从未曾设计过刚挠结合板或挠性板(图1)。 本文旨在使设计师更加了解FPC结构、FPC布局要求、FPC叠层材料的限制和极限,强调了与挠性制造商和组装厂商沟通的重要性。

图1:挠性印制电路

FPC既有刚性板的优点,又具备圆形线束电缆所不能实现的挠性、重量轻、体积小、生产成本低、电气特性一致等优点,还可用于可不断移动的动态应用中。FPC还能够弯曲、折叠或是放入三维空间中。

每家FPC制造商的设备、生产能力和操作人员都不同,而且FPC布局要求也不同。有时,挠性设计师可能需要到现场评估制造商的生产能力。

FPC设计师、制造商以及组装厂商之间的有效沟通是最终产品能否取得成功的关键。设计挠性印制电路时应遵循特定制造商的生产准则。这些准则可最大程度地减少生产技术问题,缩短澄清问题所花费的时间,以及减轻因接近生产极限而造成的性能受损和不良后果。

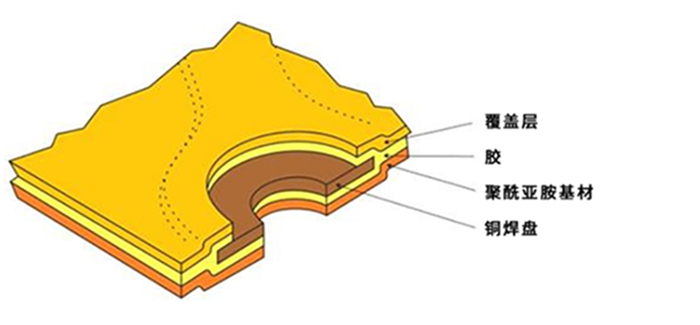

图2:1类单面有胶基材

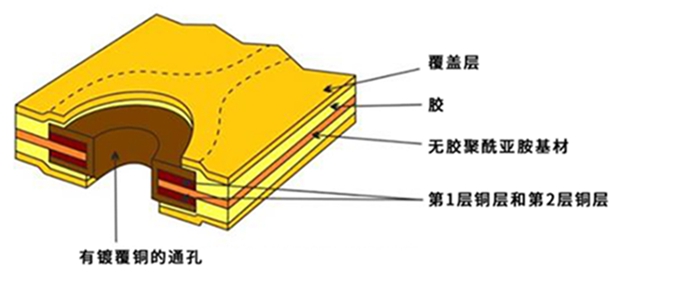

图3:2类双面无胶基材

在DFM审核期间,一系列在设计中发现的相关技术问题被称之为技术问题(technical question,简称TQ)。这类问题会降低产品的可制造水平,最终影响产品的可靠性。同一款FPC设计对于不同生产商,因为各自生产工艺能力不同,可能是标准设计,也可能是高阶设计,甚至可能是无法实现的设计。这也说明,提前了解制造商的生产能力至关重要。

生产能力会随着技术发展和生产设备改进日益提高。因此,设计准则也会相应更新。在开始布局时,FPC设计师就应该熟悉IPC标准,例如IPC-2223、IPC-2221、IPC-2222,并且了解产品级别和FPC类型。根据IPC-2223规定,有胶基材可应用于5类FPC结构,同样,无胶基材也有5类结构。图2展示了1类有胶基材和2类无胶基材。

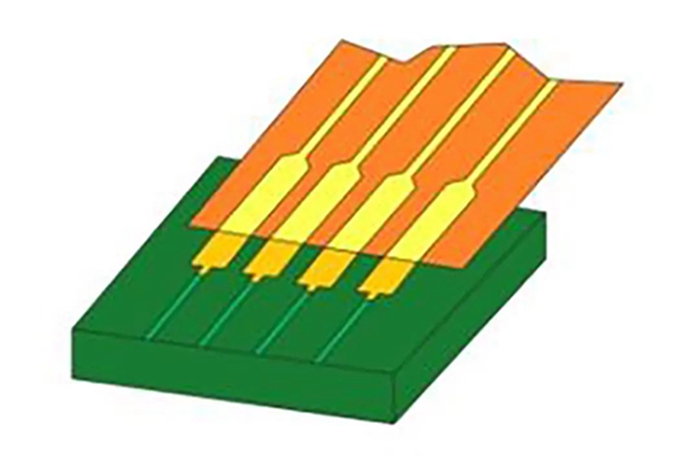

图4:热压焊接连接

挠性电路设计师应该了解最终组装要求。用B2B连接器、ZIF连接器、各向异性导电膜(ACF)可以实现刚性电路与挠性电路的连接,也可以采用热压焊接(图4)。不同技术在布局中要求的端接尺寸和形状都不一样。

挠性材料的选择和叠层,取决于预算、应用和机械限制。长期以来,聚酰亚胺都是最受欢迎的挠性层压材料。较为便宜的结构通常会采用聚酯薄膜。除了这些已被广泛使用的塑料材料,液晶聚合物(LCP)和聚萘二甲酸二乙酯(PEN)基材也是常用材料。

不论产品应用、类型和供应商的生产能力水平如何,FPC设计程序都要遵循以下基本准则:

1. 所有FPC拐角都必须是弧形的;

2. 所有走线的拐角都必须是弧形的;

3. 所有通孔、镀覆孔以及SMT焊盘与走线的连接都必须有泪滴状填充。

除了这3条准则以外,如果把SMT焊盘做成椭圆形或圆形,也是非常好的方法。或者将较大SMT焊盘的角做成弧形(图5)。

图5:从左到右分别是:拐角是弧形的走线,拐角是弧形的FPC外形,以及焊盘是椭圆形且拐角是弧形的SMT焊盘

鉴于铜会增加整个结构的刚性,设计师在布走线时应该以交错的方式分布相邻层的走线,避免大面积布铜,这种方法可以消除“工字梁效应”并提高FPC的可靠性。

降低挠性电路图形铜镀层也可以减少铜的用量。图形电镀可选择性地在焊盘上、导通孔孔壁和镀覆孔内沉积铜,该工艺需要用到Gerber文件。

挠性电路镀铜的另一种方式是全板电镀。在全板电镀过程中,铜会沉积在整个外层的铜图形和和通孔孔壁上。采用网格状铜层代替实心铜层,能够提升电路的挠性。

铜到电路边缘的距离是一个至关重要的参数,每家制造厂商使用的参数各不相同,视其生产能力而定。例如,一些生产准则规定FPC边缘与铜走线、铜层以及SMT焊盘之间的间隙为0.2 mm(8 mil)。而导通孔与FPC边缘的间隙则要求更大一些,我建议要达到0.45 mm(18 mil)。

刚入门的FPC设计师可能会使用阻焊层,而不是使用覆盖层。阻焊层非常薄,但这种材料会让挠性电路变成刚性弹簧。以下阐述了在FPC生产中为什么沟通非常重要的另一原因。

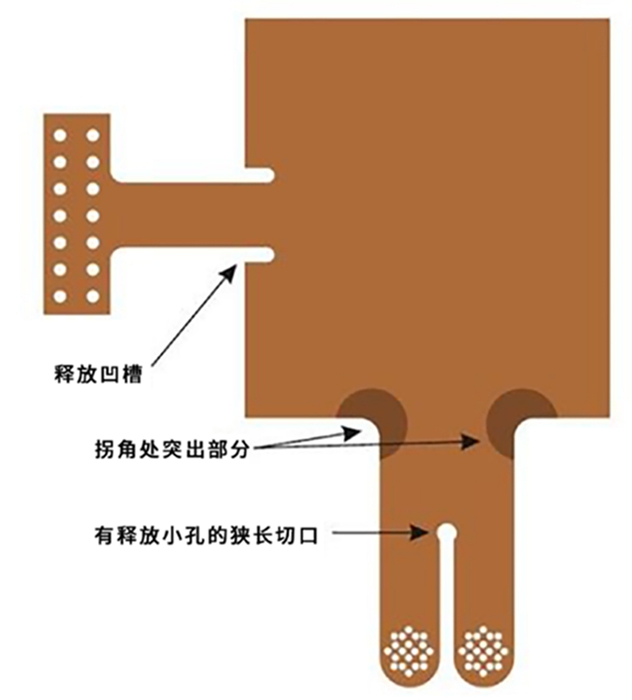

图6:减缓撕裂的方法

FPC叠层通常有介质覆盖层。覆盖层主要用于密封保护图形。但因为覆盖层相对较厚,所以与其他特征之间的间隙就要比采用阻焊层时的间隙更大。因此,设计新手应该了解FPC制造商提供的覆盖层应用的所有限制和极限。在为元器件焊盘生成余隙开口(钻或冲等)时,了解清楚采用的覆盖层材料和方法很重要。普通的生产能力需要覆盖层网与FPC轮廓之间的最小距离为0.25 mm(10 mil),覆盖层上的开口与FPC轮廓之间的距离为0.3 mm(12 mil)。细间距元器件会在覆盖层上有一组开口。

鉴于挠性电路本身就比较脆,FPC设计师在布局时应该始终考虑材料可能会撕裂的问题。图6所示是减缓撕裂的几种方法:凹槽、小孔、拐角突出部分。

FPC上的连接器区域和组装在上面的较重元器件都需要用到增强板。某些元器件聚集的位置可能也需要在元器件下方用到增强板。增强板材料可以是聚酰亚胺、FR-4,也可以是不锈钢。

但薄FPC上增强板的边缘会形成应力区域。为了避免增强板附近出现撕裂,应在增强板边缘和通孔焊盘边缘之间留出1 mm~1.8 mm的间隙,具体取决于增强板类型。必须要考虑到两个增强板之间的最小间隙。例如,顶部增强板和FPC底部第二块增强板之间的距离应该保持在0.6 mm以上。

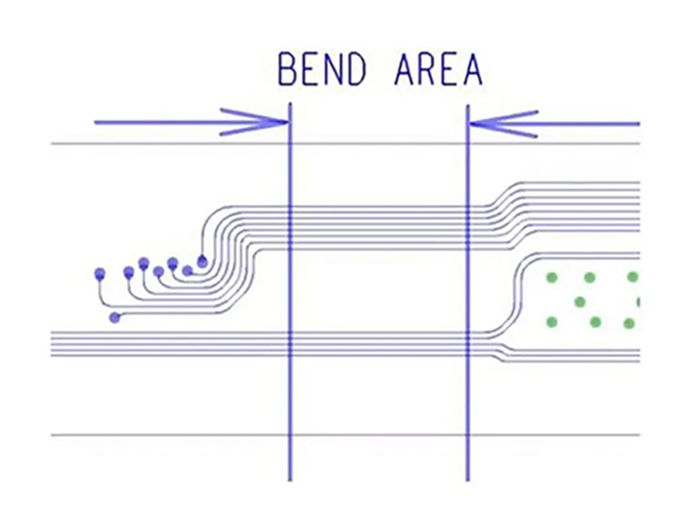

挠性电路的静态弯折区域和动态弯折区域是很难设计的。布线时走线必须要垂直于弯折区域(图7)。

图7:弯折区域的走线布线

设计师需要了解制造商生产能力范围内可以达到的最小走线宽度和间距。其中最小走线间距取决于内层铜厚度。在计算外层上的走线最小间距时,应在走线铜层厚度上加上铜镀层厚度。

高速设计通常都会包括可控阻抗。还应慎重考虑单端和差分对的参考平面。铜是会增加结构刚性的主要因素。因此,每种案例都要采用恰当的方法。如果FPC不需要弯折,则可以采用多层结构。对于动态弯折,首选FPC类型是单层收缩。但也可以使用双面无黏性基材,甚至可采用带有空气间隙的三层结构。

对于可控阻抗(微带传输线),至少要用到两个信号层,其中一层是参考平面。当可控阻抗信号层布到了动态弯折区域上,设计师需要考虑在叠层中插入空气间隙。

为了改善信号完整性,可以采用盲孔和埋孔技术。使用这类技术可以避免高速信号应用中出现通孔桩的情况。但这种生产方法会增加额外成本。

使用低轮廓加成法工艺可以生产出走线宽度和间距皆为1mil的100欧姆差分对。

对于设计高速信号,EMI始终都是隐患。这种情况下就要用到屏蔽方法。完美的EMI屏蔽层是银薄膜。薄膜厚度在22 μm~32 μm之间。当频率高于10 GHz时,必须要测试材料,因为薄膜的有效性可能会退化(图8)。

图8:屏蔽膜应用

材料的性质决定了FPC的容差非常重要。对比厚黏性覆盖层材料和薄无黏性层压板时,设计师应该明白每种材料的移动情况都有差异,在生产时也会因此遇到不同的问题。

总的来说,FPC容差比PCB容差更为宽松。生产准则中列出的所有特征都对应着相同特征的次级容差要求。FPC设计师必须要考虑到所有相关的容差,以便顺畅快速地完成生产。

与组装生产厂的合作也是至关重要的。我个人比较倾向于和那些同时具备FPC生产能力与组装能力的制造商合作。这样一来,FPC生产和组装两个领域的工作人员就更易于沟通协作,制定更全面的设计准则,更好、更快地为客户提供支持,解决问题时可在部门间实现快速高效的沟通。此外,这类工厂在处理和传送FPC时也更可靠。

总结

本篇技术文章向新手挠性设计师简要介绍了在设计产品时需要考虑到的因素及设计技巧,包括重要的挠性设计方法,以及保持FPC挠性的必要要求。

挠性设计师应始终与电气、机械、生产、组装、测试以及DFM团队的成员密切协作,这样才能保证最终产品取得成功。根据应用条件、生产具体情况、挠性材料和环境要求的不同,还会有更加具体的要求。挠性设计师必须要了解所有的生产限制和极限,并将其纳入布局设计准则当中。

作者:Olga Scheglov,CID+(IPC认证高级互连设计师),是在刚性和挠性印制电路板设计和制造领域有着20多年从业经验的电气工程师。目前在EPTAC担任CID培训讲师,已积累了11年的教学经验。