主讲人

闵潇文

毕业于荷兰埃因霍芬理工大学,取得混合信号微电子工学硕士学位。2018年加入Siemens EDA,成为电子板级系统部门的应用工程师,负责直销团队的技术支持。

在传统的DDR总线设计流程中,工程师通常遵循IC 供应商的指导手册进行布线,在完成总线布线后进行全板仿真。然而,布线后一旦发生严重的设计问题,整改和再次仿真将会花费大量的时间和力气,特别是在新的DDR5项目中。因此,Siemens EDA推荐使用渐进式的分析方式进行DDR总线的设计,增加布线前的假设性分析,并将后仿真的步骤拆分成多个步骤完成。

本次研讨会,您将了解

- 目前的DDR总线设计流程

- 现有流程中限制效率的因素

- 推荐的设计流程

- 新流程如何“工作”

-LineSim前仿真3D 过孔建模

-LineSim模板应用

-DDR 总线相关的DRC 规则

-脉冲响应分析

-DDRx Wizard 有关 DDR5 的更新

- 新流程优势总结

在传统的DDR总线设计流程中,工程师通常遵循IC 供应商的指导手册进行布线,在完成总线布线后进行全板仿真。然而这种方式缺乏布线前的设计空间探索,工程师对于设计余量把握程度不够。并且在布线后一旦发生严重的设计问题,整改和再次仿真将会花费大量的时间和力气。在最新的 DDR5 设计中,这种流程上的缺陷将被严重放大,极有可能导致项目延期和成本的损失。

.png)

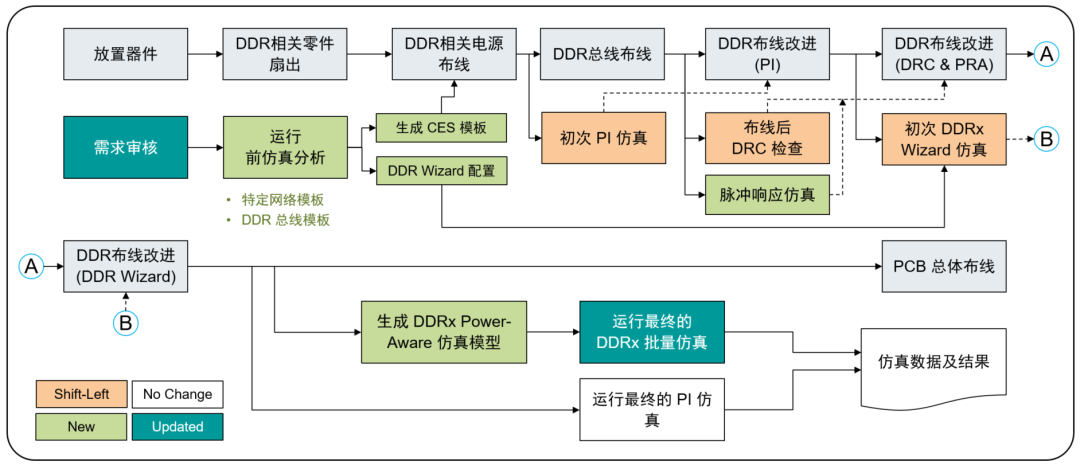

因此,Siemens EDA推荐使用渐进式的分析方式进行DDR总线设计的严重,增加布线前的假设性分析,且将后仿真的步骤拆分成多个步骤完成。以帮助工程师在更早期发现问题。我们推荐的仿真流程如下:

相比与传统的流程,我们加强了需求的审核过程,增加了布线前分析。使用 HyperLynx LineSim 在布线前就对过孔进行 3D 的建模,方便工程师精确选型和进行叠层设计。在前仿真阶段即可通过参数扫描确定有效的设计空间,增加工程师对于设计风险的把控。我们会利用模板降低应用 HyperLynx 应用的难度,并且通过 HyperLynx 生成的 CES 模板,快速在 Xpedition Layout 中定义约束。

.png)

同时建议将布线后的“一次性”仿真拆分成多个验证步骤,让设计质量可以“逐步”提高。本次研讨会中我们将介绍 DDR相关的电气规则检查,BoardSim 中新增的脉冲响应分析和 DDR5 批量仿真功能,并且通过 Hybrid Solver 与 BoardSim 环境的集成,可避免在 Power-Aware 仿真中对于 DDR 总线拓扑的搭建。

Siemens EDA 希望能帮助客户提高新一代 DDR 设备的设计效率,通过推荐的设计流程,让项目设计有效,高效,可靠。

研讨会主题

渐进式的DDR仿真

时间

2021年3月17日20:00

报名方式

扫码报名

扫码报名

来源:Mentor PCB及IC封装设计