数十年来,几乎所有的数位高速系统设计人员与制造商都面临着必须考虑高频PCB设计方面的挑战,特别是关于最佳资料转换率只可能在具有正确阻抗率的传输路径上实现。电缆和连接器的时域阻抗曲线一直都是一项非常重要的指标。时域阻抗曲线可以指示特性阻抗、延迟等特性,也可以反映由阻抗不连续、衰减、偏移等引起的反射等传输问题。时域反射法 (TDR) 阻抗最初是一种测量技术。后来随着工作频率的提高,需要进行详细的电气仿真,因此获取完整的 S 参数测量是必要的,并且由连接器供应商提供 TDR 结果和 S 参数。

如今,TDR阻抗特性对于设计人员而言仍然非常重要。并且在频域、时域、阻抗域三种电学基本特性测试测量仪器中,阻抗域测试测量仪器所用电路结构最复杂、测试操作最费时间、成套价格最高。目前能够供应GHz级阻抗域测试测量仪器的公司为数不多。

在目前的大多数情况下,我们通常通过 S 参数计算得到TDR阻抗特性。但为节省处理时间和磁盘空间,采样得到的测量的 S 参数数据往往仅够正确地表示连接器的延迟,而提高采样频率则达不到给定数据速率下奈奎斯特标准的要求。所以在根据测量的 S 参数计算时域阻抗曲线时,我们会面临下面两种类型的问题。

S 参数质量较差

目前生产中采样的 S 参数质量较差,例如分辨率不足、频带限制、噪声等。这些参数问题造成了某些数值计算起来比较困难,例如响应混叠、振铃和非因果关系。这使得计算得到的阻抗受连接器远端设置的端接条件影响较大。在 TDR 阻抗计算中,我们常采用两倍的连接器延迟,这使得 S 参数的采样率更加不足。

反射掩盖“真实”值

即使使用理想数据,计算出的阻抗曲线也无法显示连接器各部分的正确特性阻抗,因为多次反射会掩盖远端部分特性阻抗的“真实”值。我们在阻抗图中观察到的特性阻抗如果被具有不同特性的区段所掩蔽,可能并非传输线的实际特性阻抗。

在Siemens EDA的白皮书中,我们介绍了根据频率特性计算时域响应的两种方法,一种是目前常用的,使用回波损耗的离散傅里叶逆变换 (IDFT),但该方法没有考虑到由于阻抗不连续导致的多次反射,这可能导致错误的阻抗曲线结果。另一种是采用直接时域计算的复极点拟合,样本频域函数被“拟合”并表示为递归特征消除(RFE) 的形式。通过比较基于 IDFT 和 RFE 的方法,我们发现它们都不完美,但通过结合两者的优势可以获得最佳质量的解决方案。通过使用这两种方法,对离散傅里叶逆变换 (IDFT) 结果进行后处理或矢量拟合,我们可以对结果进行交叉验证,解决S参数质量较差的问题,更好地进行阻抗曲线的计算。

.jpg)

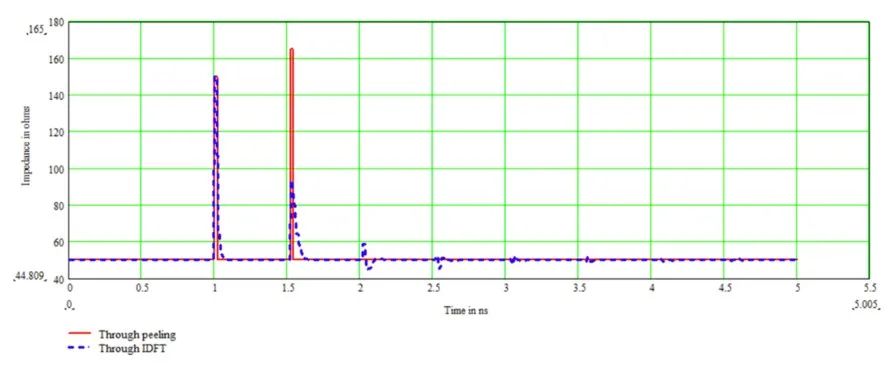

除此之外,在白皮书中Siemens EDA提出了一种计算阻抗曲线的替代方法,将被测设备 (DUT) 建模为多个较小传输线的级联连接,并应用时域门控和剥离技术,以计算每条传输线的长度和阻抗, 使得合并的级联系统的阻抗曲线等同于 DUT 的阻抗曲线 。该方法将逐次计算一小部分的阻抗,从而实现在继续计算后续部分的阻抗之前撤消这一小部分的影响,这种算法可以考虑到由于阻抗不连续而导致的多次反射,从而减少误差。通过验证,与 IDFT 方法相比,该算法可以给出准确的结果。

(红色使用所提出的算法。蓝色使用 IDFT 方法。IDFT 方法在阻抗曲线 1.52 ns 左右的位置给出了错误的值。)

点击这里下载完整白皮书

来源:Mentor PCB及IC封装设计