当信号过孔通过空腔时,可能发生耦合。遗憾的是,这种阻抗源往往被忽视,导致出现难以诊断的 PDN 问题。

低阻抗 PDN 对于保持足够的电流输送至接收器,并最终确保印刷电路板 (PCB) 具有适当的性能至关重要。虽然有一些一般设计指导准则可帮助实现低阻抗,但能够完全遵循这些指导准则的情况很少。因此,了解 PDN元器件如何影响其阻抗曲线非常重要。

本文中的例子说明了添加空腔元件,例如稳压器模块(VRM)、去耦电容和缝合孔,如何影响空腔阻抗,介绍了添加 VRM、去耦电容和缝合孔如何降低空腔在不同频率范围的阻抗曲线。减小空腔的厚度会进一步降低其阻抗,使得薄腔的阻抗不受电容器的位置影响。我们还探讨了使用对信号返回路径尽可能透明的 PDN 空腔的重要性。

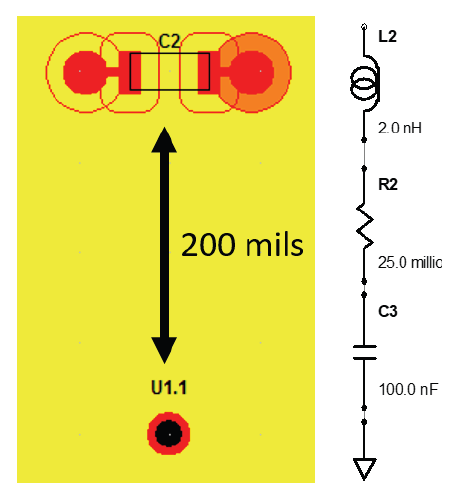

图1:去耦电容安装方式

点击这里即可获取完整白皮书哦~

来源:西门子EDA

标签:

#PCB

#Design

#设计

#Mentor

#白皮书

#免费下载

#电源完整性

#概念

#PDN

#元件

#阻抗

#影响